Page 2 of 5

Re: Q68 Notice 3 - Update

Posted: Wed Nov 15, 2017 5:22 pm

by johnh

Hi, Derek.

Please add my name to the list for one of the second batch (Q68 + case + splitter).

John Hall

Re: Q68 Notice 3 - Update

Posted: Wed Nov 15, 2017 5:35 pm

by Zarchos

Peter wrote:martyn_hill wrote:In due course, would live to hear more about the spec of the expansion connector - one of the 'features' of the original QL that keeps me glued is the simplicity of designing add-ons using 8-bit, legacy speed components, prototyped on a breadboard or wire-wrapped. One day I might grow-up and enter the world of SMD and proper PCB design, but until then, my tinkering will remain old-school...

The Q68 contains only a minimalistic extension bus with 8 bit data and 8 bit address bus. Suitable for peripherals, but not memory. The voltage levels are 3.3V. Nowadays this should be easier to use that 5V, even for tinkering. Because of the small board size, the spacing of the pads is 2 mm, not 2.54 mm. Okay for connectors or wire soldering, but not suitable for standard IDC cables.

In the Q68 memory map, the extension bus is located at $1D800..$1DFFC. The extenal lines A0...A7 are internally connected to A2...A9 of the CPU, accessible every 4th byte (longword-aligned). This is to make driver adaption to/from 32 bit bus systems like Q40/Q60 easier.

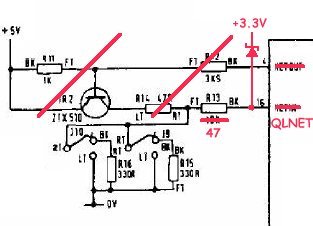

The extension bus also provides a signal for singlewire networking (QLNET) with few external components. This has no software support yet.

We decided not to solder any connector for the extension bus, because no professional add-on cards are in sight. For tinkerers, soldering a socket, or direct wiring should be easy enough.

Due to the already decoded chip select signal, the design of simple add-ons should be even easier than for the QL. And signal quality is better because of short lines and continuos ground plane. Timings are "legacy speed", but I may not find time to write detailed specifications anytime soon. I have never even tried the extension bus myself, other than for the Q68 ethernet controller, which is on the same bus.

extbus.jpg

Reading this I have the feeling using a Rpi as an extension shouldn't be that difficult. Very interesting.

Re: Q68 Notice 3 - Update

Posted: Wed Nov 15, 2017 5:49 pm

by martyn_hill

Thanks Peter - sounds promising!

Glad to hear that QLNET is still in mind, even if not implemented yet

Re: Q68 Notice 3 - Update

Posted: Wed Nov 15, 2017 7:05 pm

by Peter

QL NET is using the same hardware registers as the QL. But due to the differences in CPU speed, new timing loops are needed.

With a lot of help from W., we started on this, but there was too much other work. Maybe others want to finish it.

Meanwhile, the Q68 got a high-resolution timer, 25 ns per tick. So it could now make sense to implement the QL NET directly by specification instead of using instruction timing loops.

Re: Q68 Notice 3 - Update

Posted: Wed Nov 15, 2017 10:46 pm

by martyn_hill

Now, there's a provoking proposition...

I've spent quite some time reverse engineering QLNET (if you can call it that - the present documentation and availability of source code went a long way) - whilst developing the QLUB adapater (still in progress...) and would gladly team-up to assist with a modified Q68 driver and ideas for implementing the network

Re: Q68 Notice 3 - Update

Posted: Thu Nov 16, 2017 9:55 am

by Peter

Sounds good, and Q68 SMSQ/E will be open source of course.

QL NET seems still the best connectivity with the original QL. From Q68 to Q68, SERNET at 115 kBaud over Nullmodem cable is fine. But on the original machine, SER remained problematic.

The picture below shows the Q68 network wiring in comparison to the QL schematics. Looking back, I should of course have added the few components directly on the Q68 PCB. But at design time, it seemed unlikely that someone would write the driver. Could you solder that?

- qlnet.jpg (16.96 KiB) Viewed 4212 times

Re: Q68 Notice 3 - Update

Posted: Thu Nov 16, 2017 10:01 am

by stewie

Hi Derek

I’m definitely interested, can you add me to you second batch list with case and splitter

Cheers Stewart

Re: Q68 Notice 3 - Update

Posted: Thu Nov 16, 2017 10:16 am

by Pr0f

Peter wrote:Sounds good, and Q68 SMSQ/E will be open source of course.

QL NET seems still the best connectivity with the original QL. From Q68 to Q68, SERNET at 115 kBaud over Nullmodem cable is fine. But on the original machine, SER remained problematic.

The picture below shows the Q68 network wiring in comparison to the QL schematics. Looking back, I should of course have added the few components directly on the Q68 PCB. But at design time, it seemed unlikely that someone would write the driver. Could you solder that?

qlnet.jpg

So from the diagram does that mean your network pin is bi directional, and only the termination resistors are required ? I see the schottky diode to VCC to take positive going transients, what rating does that have to be to cope with the original QL network being referenced to 5V VCC ?

Sorry for all the questions Peter...

Re: Q68 Notice 3 - Update

Posted: Thu Nov 16, 2017 11:00 am

by Peter

Yes the line is bidirectional. The clamp diode to 3.3V should be schottky. In combination with the 47 Ohms series resistor, it protects the 3.3V logic of the Q68.

Clamping to 3.3V with the two 47 Ohms series resistors at each end should not have any negative effect for the QL. The input voltage level requirements are met. One or two Q68 inside an original QL network caused no problem here. Viewed on oscilloscope, this "soft" clamping even seemed to improve signal quality a little when cables were long.

Re: Q68 Notice 3 - Update

Posted: Thu Nov 16, 2017 12:39 pm

by martyn_hill

Hi Peter!

OK, we're on... Just to be clear, the components still needed include everything in the green mark-up I've added below?

- qlnet_q68_markup.jpg (48.4 KiB) Viewed 4162 times

Do you have any preferences/existing ideas for how we would make the connection to those pads on the Q68 PCB? For example, we wouldn't want to block further expansion by hogging the pads-area...

M.